Tin tức

Cha đẻ Linux lại xỉ vả Intel, vì làm một linh kiện máy tính quan trọng gần như “tuyệt chủng”

Theo ông Linus Torvalds, vì chính sách của Intel, loại RAM ECC đã gần như tuyệt chủng trên thị trường máy tính dành cho người dùng thông thường, dù nó cũng rất quan trọng.

Dù vài năm trước, Linus Torvalds, người sáng tạo nên nhân Linux phổ biến hiện nay, từng tuyên bố rằng, mình sẽ cố gắng kiềm chế tính cách cộc cằn của bản thân để trở thành một người hành xử chuyên nghiệp khi làm việc với người khác, nhưng dường như Intel đã làm ông phải phá bỏ cam kết của mình.

Vào đầu tháng Một này, trong một bài đăng trên trang realworldtech, ông Linus đã không ngớt lời chỉ trích thẳng mặt Intel khi xem họ là nguyên nhân chính dẫn đến sự thiếu hụt của một linh kiện quan trọng trong máy tính, RAM ECC (Error Correcting Checksum) – hay RAM tự sửa lỗi. Quan trọng hơn cả, vì Intel, người dùng thông thường còn không biết đến sự tồn tại của linh kiện này.

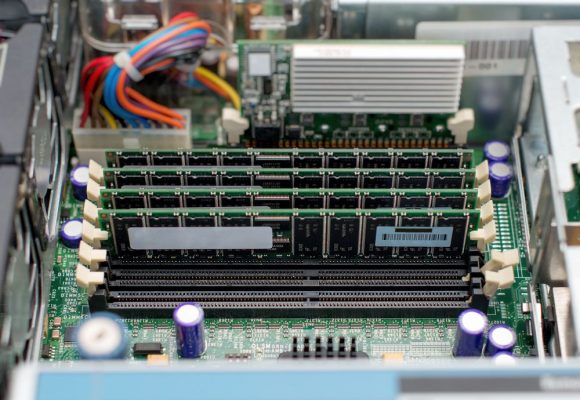

Nếu bạn là người hay phải lên thông số cho phần cứng máy chủ, ví dụ như các CPU, các bản mạch chủ dành riêng cho máy chủ, bạn sẽ biết đến loại RAM ECC này. Về bản chất, RAM ECC sẽ chứa một mẩu bộ nhớ vô cùng nhỏ dùng để phát hiện và chỉnh sửa các lỗi trong bộ nhớ.

Tại sao tính năng ECC lại cần thiết?

Trong hầu hết các bộ nhớ hiện tại, cứ mỗi một từ 64-bit được lưu vào trong RAM, sẽ có 8 bit kiểm tra. Nếu một bit bị lỗi – ví dụ số 0 bị nhảy thành 1 hoặc số 1 đổi thành 0 – sẽ bị phát hiện và tự động sửa lại. Còn nếu có 2 bit bị nhảy trong cùng một từ, chúng có thể bị phát hiện ra nhưng không được sửa. Còn nếu có 3 bit hoặc nhiều hơn nữa bị nhảy trong cùng một từ, chúng vẫn có thể bị phát hiện, nhưng không hoàn toàn đảm bảo.

Có rất nhiều lý do cho lỗi nhảy bit này, có thể là vì tia vũ trụ hoặc có thể vì lỗi ngẫu nhiên của phần cứng. Một nghiên cứu về máy chủ của Google cho biết, khoảng 32% máy chủ (và 8% trong các bộ nhớ DIMM) của Google gặp phải ít nhất 1 lỗi bộ nhớ mỗi năm. Phần lớn trong số đó là lỗi một bit – và do Google sử dụng các CPU dành cho máy chủ và RAM ECC, các cỗ máy của họ có thể tự sửa lỗi và tiếp tục hoạt động như bình thường.

Trong khi đó, đối với các máy tính của người dùng, dữ liệu của Google cho thấy, các lỗi nhảy một bit này có khả năng xảy ra cao gấp 40 lần nhảy nhiều bit. Mặc dù vậy, vì không dùng đến các RAM ECC như Google, các lỗi này không được phát hiện ra và có thể làm hệ thống thiếu ổn định cũng như hỏng dữ liệu.

Việc nhảy bit không phải lúc nào cũng ngẫu nhiên

Không phải mọi lỗi trong RAM đều ngẫu nhiên do lỗi phần cứng hay các sóng điện từ EMF. Trong những năm gần đây, các nhà nghiên cứu phát hiện ra ngày càng nhiều các cuộc tấn công kênh phụ (side channel attack) thông qua việc tiếp cận vật lý tới hệ thống.

Từ việc sử dụng lỗi nhảy bit một cách có điều khiển trong những khu vực RAM có thể tiếp cận tới một ứng dụng nào đó, kẻ tấn công có thể suy luận ra hoặc chỉnh sửa các giá trị dữ liệu trong các vùng RAM đáng nhẽ họ không thể tiếp cận.

Cho dù RAM ECC không thể giảm nhẹ cuộc tấn công theo dạng RAMBleed này, nhằm suy luận giá trị dữ liệu trong các khu vực lân cận bộ nhớ, nói chung nó có thể ngăn cuộc tấn công kiểu Rowhammer (kiểu tấn công bằng cách truy cập liên tục vào một vị trí trên DRAM để gây lỗi nhảy bit, có thể thực hiện từ xa) khi làm hệ thống bị tắt mà không ảnh hưởng gì đến dữ liệu. (Phần lớn các hệ thống dùng RAM ECC được cấu hình để dừng hoạt động hoàn toàn nếu phát hiện ra một lỗi không thể sửa được).

Tại sao lại là Intel?

Thế nhưng rất ít người dùng thông thường biết đến sự tồn tại của RAM ECC và theo Torvalds, đó là lỗi của Intel.

Đã từng có thời bạn mua một CPU thông thường, nhưng vẫn được hỗ trợ RAM ECC, nhưng đó là câu chuyện của 15 năm trước với các chipset 975X. Sau đó, tính năng này chỉ được Intel trang bị cho các dòng CPU máy chủ như Xeon. Lập luận của Intel chỉ đơn giản là “người tiêu dùng không cần đến ECC”.

Nhưng như các lý do kể trên, những cuộc tấn công kiểu Rowhammer và các lỗi nhảy bit vẫn tiếp tục diễn ra – điều đó chứng tỏ người dùng thông thường cũng cần đến nó – không như tuyên bố của Intel. Không có sự hỗ trợ từ CPU Intel – vốn là hãng có vị thế gần như độc quyền trong nhiều năm nay – các RAM ECC dành cho người dùng thông thường cũng vì thế dần biến mất.

“Và các nhà sản xuất bộ nhớ sẽ nói rằng nó là vì tính kinh tế và hiệu năng thấp. Và họ là những thằng khốn dối trá – hãy nhìn vào cuộc tấn công kiểu Row-hammer để thấy vấn đề này đã tồn tại từ nhiều thế hệ nay, nhưng những kẻ khốn này vẫn vui vẻ bán phần cứng hỏng cho người dùng và nói rằng đó là một cuộc “tấn công”, khi nó vẫn luôn hiện diện ở đó.”

“Đã bao nhiêu lần các lỗi nhảy bit tương tự như cuộc tấn công Rowhammer xảy ra chỉ vì vận đen rơi đúng vào tải công việc chứ không phải bị tấn công? Chúng ta sẽ không bao giờ biết được. Bởi vì Intel đã đẩy phần thiệt đó về người dùng.”

Nhưng tại sao Intel lại làm vậy? Theo ông Torvalds, đó là cách Intel phân khúc thị trường của mình. Các CPU dành cho người dùng thông thường với giá rẻ hơn và lợi nhuận thấp hơn, nhưng lại thiếu các tính năng bảo vệ cần thiết như ECC, sẽ không giẫm chân lên các CPU máy chủ – vốn đắt đỏ hơn và nhiều lợi nhuận hơn – khi hướng tới các doanh nghiệp lớn.

Thông thường, người ta cho rằng chi phí là nguyên nhân các phần cứng hỗ trợ ECC hiếm khi dành cho người dùng thông thường. Tuy nhiên, hãy nhìn vào các RAM ECC. Ngay cả khi chúng rất khó tìm mua được, giá bán lẻ của chúng cũng chỉ cao hơn khoảng 20% so với giá RAM thường. Tuy nhiên vấn đề lại là, nếu các bản mạch chủ và CPU không hỗ trợ nó, lắp ráp RAM ECC cũng không mang lại lợi ích gì.

Về lý thuyết, dòng CPU Ryzen của AMD cũng hỗ trợ ECC, dù không chính thức. Nhưng chính vì vậy, điều này cũng không có gì đảm bảo các nhà sản xuất các linh kiện khác, như bo mạch chủ, hoặc các nhà OEM sản xuất máy tính, hỗ trợ tính năng này – ngay cả khi họ đã tuyên bố như vậy. Cách duy nhất chắc chắn một bo mạch chủ Ryzen nào đó tương thích với ECC là chạy một ứng dụng nào đó gây ra lỗi nhảy bit để kích hoạt tính năng đó.

Một hy vọng khác với người dùng là RAM DDR5 đang bắt đầu ra mắt trong năm 2020. Bên cạnh các cải tiến về dung lượng, băng thông và sức mạnh, điều đáng chú ý là các mã tự sửa lỗi ECC sẽ được nhúng ngay trong chip nhớ. Khi đó, sự phổ biến của thế hệ RAM mới này có thể sẽ kéo theo sự hỗ trợ rộng rãi hơn từ các linh kiện khác như bo mạch chủ.

Tham khảo ArsTechnica